# Sistema embebido para la detección de luz láser empleando el soft-core Nios II

Julio C. Sosa<sup>1</sup>, Iván Dominguez-López<sup>2</sup>, Adrián L. García-García<sup>2</sup>, J.D. Oscar Barceinas-Sánchez<sup>2</sup>, Anuar Jassen<sup>2</sup>

<sup>1</sup> Instituto Politécnico Nacional, Escuela Superior de Cómputo, México. D.F., México

> <sup>2</sup> Instituto Politécnico Nacional, CICATA, Querétaro, Qro. México

{jcsosa, idominguezl, agarciag, obarceinas}@ipn.mx

**Resumen.** Un sensor lineal CCD o CMOS es un componente esencial en muchas aplicaciones de la ingeniería y del consumo. En este trabajo se presenta la primera etapa del diseño y desarrollo de un sistema embebido para monitorear la distribución angular de la intensidad de luz láser. Se presenta la finalidad del desarrollo de ese trabajo y se muestran los primeros resultados del sistema, el cual emplea un sensor de visión lineal CCD con 3,648 píxeles y es controlado con el soft-core Nios II de Altera. Para el diseño e implementación se utilizó Quartus II software y el FPGA Cyclone IV, de Altera. Se empleó sólo el 26% de los elementos lógicos y 4 de los 132 multiplicadores embebidos (3%), del FPGA.

Palabras clave: CCD, FPGA, sistema embebido, Nios II, LLS.

# **Embedded System for Lazer Light Detection Using Softcore Nios II**

**Abstract.** A CCD or CMOS linear sensor it's an essential component in various applications of engineering and consume. In this work we will present the first stage of the design and development of an embedded system for monitoring the angular distribution of the intensity of a laser light. It is presented the purpose of developing this work and it is shown the first results of the system, which makes use of a linear vision sensor CCD with 3,648 pixels, this is controlled by the softcore Nios II from Altera. For the design and implementation it was used the software Quartus II and the FPGA Cyclone IV both from Altera. Only the 26% of the logic elements and 4 of the 132 embedded multipliers (3%) of the FPGA were used.

Keywords: CCD, FPGA, embedded system, Nios II, LLS.

#### 1. Introducción

Desde hace algunas décadas la importancia económica de la tribología ha tomado un gran interés. Esto es debido, por ejemplo, a que el desgaste es la principal causa de que los bienes materiales pierdan su utilidad [1].

La metodología empleada para el estudio del desgaste adhesivo, utilizando un tribómetro de perno en disco, se basa en la norma ASTM G-99-05 [2]. Esta norma establece que el resultado de la prueba se obtiene estrictamente a posteriori. Esto significa que no es posible llevar a cabo mediciones de contacto durante el desarrollo de la prueba. Al existir esta limitación es importante el desarrollar metodologías que permitan el estudio y detección del desgaste in situ y en tiempo real. Por esta razón, ha habido un gran interés en la aplicación de técnicas ópticas no destructivas, ya sea en la investigación o en la industria. En años recientes se ha utilizado la luz láser para el monitoreo de procesos de desgaste en tiempo real [3].

Para determinar el esparcimiento de luz láser o LLS (Laser Light Scattering) se emplea un esparcímetro; los elementos que lo conforman son: a) el emisor laser, b) la muestra bajo análisis, y c) el detector [4]. Bajo condiciones específicas del arreglo óptico es posible conseguir que la luz láser esparcida por la superficie caiga a lo largo de una línea recta [5], la resolución en la medición de la distribución angular de la LLS dependerá directamente del número de fotodetectores por lo que se requiere un arreglo lineal, con un gran número de fotodetectores.

En este trabajo se presenta el diseño para el control y sensado de la luz láser y una etapa de adquisición con una interfaz para la transmisión hacia un computador. Para ello se emplea: un arreglo lineal de sensores CCD, un procesador soft-core Nios II, embebido en un dispositivo lógico programable del tipo FPGA y la interfaz UART. Además de eso, se presenta la interfaz de usuario, la metodología de diseño, arquitecturas embebidas existentes para la etapa del sensado y el prototipo de diseño experimental.

#### 2. La técnica LLS y los sistemas embebidos

## 2.1 Técnica de luz láser esparcida o LLS

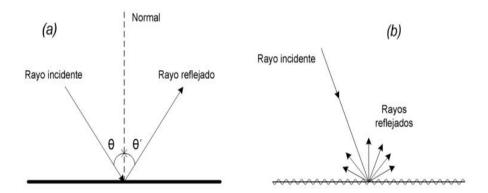

El trabajo final consistirá en emplear la técnica LLS, la cual consiste en colocar el láser al ángulo de análisis y hacer que el detector recorra una trayectoria circular. Estos ángulos son referidos a la normal de la superficie. En una superficie idealmente lisa, Fig. 1a, todo el haz será reflejado sólo en dirección a la especular. En una superficie real, Fig. 1b, cualquier imperfección producirá el esparcimiento de luz láser, que será proporcional a los defectos de la superficie de la muestra [4].

Fig. 1. Reflexión de la luz en una superficie ideal (a) y real (b).

Puesto que la luz láser se esparce en todas direcciones, después de incidir en la muestra de estudio, el detector puede ubicarse en el sitio más conveniente. Esta flexibilidad le confiere a la técnica LLS la posibilidad de adaptarse a varios sistemas tribológicos de interés para la industria [1].

Aunque en este trabajo, la técnica será utilizada para determinar o medir especificaciones de rugosidad, esta técnica también es utilizada con otros propósitos. Por ejemplo, en [6], es empleada para la medición del contenido de proteína en la leche descremada.

En [7], se utiliza para determinar especificaciones de rugosidad y para ello emplean un arreglo de fotodiodos y monitorean la distribución angular de intensidad de luz láser esparcida. La razón que exponen, del uso del arreglo de fotodiodos, es para disminuir la cantidad de datos a procesar.

En este trabajo se emplea un sensor lineal CCD con 3648 píxeles. Cada píxel tiene un grosor de 8  $\mu$ m  $\times$  200  $\mu$ m. El dispositivo es un Toshiba TCD1304AP [8].

#### 2.2 Sistemas embebidos

Un sistema embebido es un sistema digital conformado por hardware y software y es diseñado para realizar una o varias tareas específicas [9]. En sí, los sistemas cuentan con una unidad central de procesamiento (CPU) la cual se encarga de realizar los cálculos para la tarea especificada. Una vez, con la información adquirida, por medio del sensor de visión lineal CCD y con el cálculo, se pueden accionar actuadores para realizar una tarea o bien se envían los datos adquiridos y procesador a un módulo principal que contenga y administre toda la información, como es en este caso.

Para el diseño del sistema embebido existen distintas arquitecturas, las cuales se pueden clasificar en función del tipo de dispositivo principal: las basada en un microprocesador [10], las basadas en un microcontrolador [11], las basadas en un procesador digital de señales (DSP), las basadas en un chip hecho a la medida (SoC) y las basadas en un dispositivo lógico programable (PLD) [12].

# 3. Diseño de la arquitectura

#### 3.1 Metodología de diseño

Para el diseño de la arquitectura se parte de los componentes que se van a emplear, la necesidad de un posible rediseño y la arquitectura y dispositivo a emplear. De esta manera se elige la metodología de diseño más apropiada para el sistema embebido.

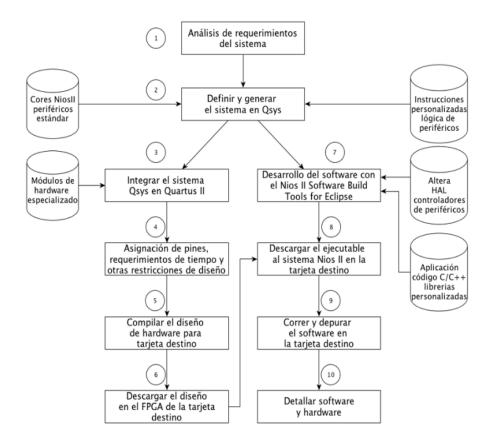

Se propone que el sistema pueda alcanzar en un futuro velocidades de trasmisión mayor a 12Mbps. La razón es que si bien ahora sólo se implementará la etapa de detección de luz láser, en un futuro se contempla sensar más señales o variables. Por ello se empleará para el diseño un PLD del tipo FPGA. Entonces el flujo de diseño es el mostrado en la Fig. 2, y es llamada metodología FPGA [13].

Fig. 2. Flujo de diseño de la metodología FPGA.

Se plantea utilizar un FPGA de la compañía Altera. En particular será la FPGA Cyclone IV EP4CE22F. Dicho dispositivo está montado en la tarjeta de desarrollo DE0-Nano, mostrada en la Fig. 3.

**Fig. 3.** Tarjeta de desarrollo DE0-Nano, de  $7.5 \times 5$ .

La elección de la tarjeta, es debido a varias características, entre las que destacan: una FPGA con 22 elementos lógicos, 32 MB de memoria SDRAM, 2 KB de EEPROM, un convertidor analógico-digital (CAD) de 8 canales, de 12 bits y una dimensión de 7.5  $\times$  5.

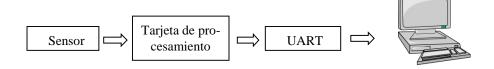

#### 3.2 Arquitectura propuesta

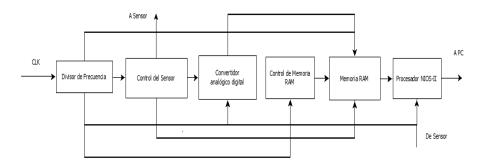

Se propone una arquitectura basada en cuatro bloques, como se muestra en la Fig. 4. El primero es una tarjeta que integra la etapa de configuración del sensor de visión lineal CCD. Un segundo módulo para la adquisición, adecuación a señal digital, procesamiento de la información y el control de la señal para la comunicación hacia la computadora. El tercer módulo, consiste en la adecuación de la señal para su transmisión vía el UART. Finalmente, se tiene un computador, donde se registrarán los datos y estos podrán ser monitorizados. Aquí se diseñará la interfaz de usuario para seleccionar el puerto COM a utilizar y sea posible mostrar en pantalla las lecturas del sensor CCD.

Fig. 4. Diagra a bloques del sistema propuesto.

## 3.3 Etapa del sensor

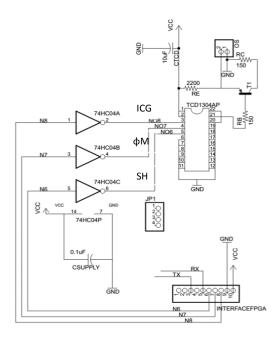

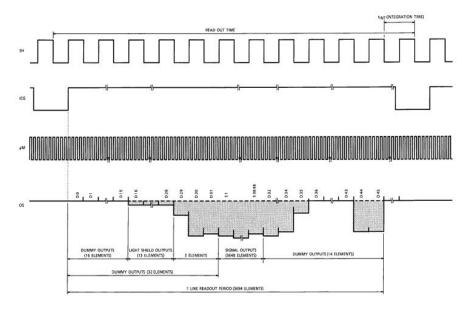

En etapa se realiza la configuración proporcionada por el fabricante [8], como se muestra en la Fig. 5.

Fig. 5. Configuración del sensor de visión lineal TCD1304AP.

La configuración consiste en acondicionar las señales de control, Integration Clear Gate (ICG), Shift Gate (SH) y el Master Clock ( $\phi$ M), mediante tres inversores. Estos inversores están dentro del circuito 74HC04. Notese que debajo de los inversores están las conecciones de alimentación y tierra de dicho circuito integrado. Además de esto se recibe la salida Signal Output Voltage (OS) que es manejada por el transistor 2SA1015. La salida está en la terminal 2 del conector OS. Las señales SH,  $\phi$ M e ICG son proporcionadas y controladas por la tarjeta de procesamiento, DE0-Nano.

#### 3.4 Tarjeta de procesamiento

Esta tarjeta tiene como componente principal la FPGA Cyclone IV EP4CE22F17C6N, de Altera; un CAD NS ADC128S022, de 8 canales y 12 bits A/D; y un banco de memoria externa SDRAM de 32 MB.

Las señal de salida del sensor CCD OS, de generación y control SH, φM, ICG, además de las señales de la interfaz UART RD y TD, son proporcionadas por la tarjeta DE0-Nano. Las señales, SH, φM e ICG, son las terminales *GPIO\_2[0]*, *GPIO\_2[2]* y *GPIO\_2[4]*, respectivamente y la salida del sensor CCD (OS) es la terminal *Analog\_In0*, todas del conector JP3. Por otro lado, las señales de comunicación RD es la *GPIO\_1[5]* y TD la *GPIO\_1[7]*, del conector JP1. El lenguaje de descripción de hardware utilizado para el diseño fue Verilog y la herramienta de desarrollo fue *Quartus II software*, web edition versión 13.0 con sp1.

La arquitectura para controlar estas señales, además de las necesarias para almacenar datos y transferir la información a la PC, está constituida por 6 bloques básicos, como se muestra en la Fig. 6.

**Fig. 6.** Diagrama a bloques de la arquitectura en la FPGA, para el manejo y control de las señales que intervienen en el sistema.

El primer bloque, de izquierda a derecha de la Fig. 6, es un divisor de frecuencia. El segundo bloque genera las señales necesarias para el control del sensor CCD. Para el diseño del módulo se empleó el diagrama de tiempos, mostrado en la Fig. 7, en donde indica en qué momento se activa cada señal [8].

Los dos bloques siguientes, tercero y cuarto, son los que gestionan el CAD y la dirección para almacenar en una memoria RAM interna. El quinto boque es la memoria RAM interna de 4 KB. El último bloque, es un procesador Nios II, que controla y gestiona la información de toda la arquitectura. Así mismo, funciona como un estándar de interconexión con la computadora, al cual le fue programado el protocolo UART en el procesador. Esto quiere decir que: primero al FPGA se le configura la arquitectura, todos los bloques de la Fig. 6, incluyendo el procesador Nios II. Después, el procesador Nios II es programado para que realice la gestión y el control de todo el sistema. Para su programación fue empleado el software Nios II SBT, para Eclipse [14].

Fig. 7. Configuración del sensor de visión lineal TCD1304AP.

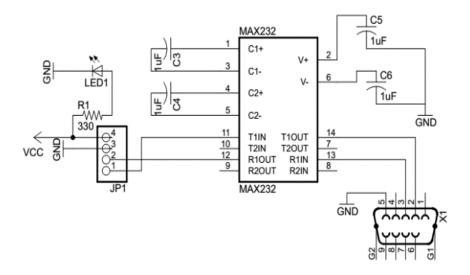

#### 3.5 Universal Asynchronous Receiver Transmitter (UART)

Esta etapa consiste en la adecuación de los niveles de voltajes de la computadora TTL y los niveles de +12 y -12 del estándar UART. Además de realizar la transferencia de información por este medio de comunicación. Para ello se empleó un MAX232 [15] y los componentes necesarios para su implementación, como se muestra en la Fig. 8.

Fig. 8. Max 232 y los componentes para su implementación.

Para realizar la comunicación hay que indicar los parámetros de velocidad en baudios, número de bits por carácter, tipo de paridad y número de bits de paro, todo en un Byte. Los tres primeros bits más significativos (7:5) indican la velocidad en baudios, que puede ir desde los 110 baud (000) hasta los 9600 baud (111). Los dos siguientes bits indican si se trabaja con paridad par, impar o sin paridad. El bits 2 indica si hay 1 bit de parada (0) o si son dos bits de parada (1). Finalmente los bits 1 y 0 indican el número de bits de datos.

Las salidas del RS232 van conectadas a un conector DB9. Por ello es necesario un cable DB9 → USB, que se conectará entre el conector DB9 y uno de los puertos USB del computador.

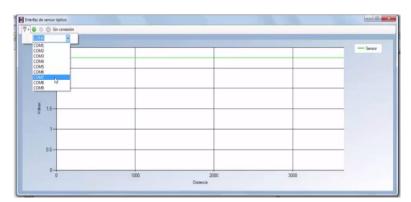

#### 3.6 Interfaz para la PC

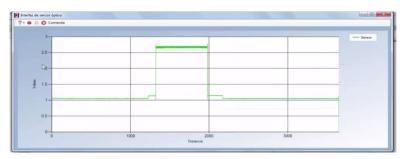

La interfaz para la PC, desarrollada con Visual Estudio, consiste en una ventana en la que permite seleccionar el puerto COM, por el que se introducirá la información que proviene de la tarjeta DE0-Nano. Para ello se utiliza uno de los puertos USB de la computadora. Este puerto contendrá los datos de recepción y transmisión (RD y TD) que envía la tarjeta DE0-Nano a una velocidad de 9600 baud. Estos datos servirán para procesar y visualizar la información en la pantalla de la PC. La interfaz se muestra en la Fig. 9.

Fig. 9. Interfaz de visualización de la señal sensada por el CCD.

#### 4. Pruebas

Debido a la sensibilidad del sensor detectada se realizaron tres pruebas, una sin iluminación (nocturna), otra de día y con iluminación artificial y una tercera que fue obstruyendo con una franja de papel al sensor de luz. Para monitorear los datos y que correspondieran con los que se grafican en la pantalla se empleó un osciloscopio, como se muestra en la Fig. 10. La primera prueba fue nocturna, con el fin de evitar la iluminación del día y de luz artificial y se empleó una videocámara para registrar la información, como se muestra en la Fig. 10 a).

**Fig. 10.** a) Interfaz y osciloscopio sin luz en el medio ambiente. b) Señales en la interfaz y osciloscopio, tomadas durante el día y con luz artificial.

La segunda prueba, mostrada en la Fig. 10 b), se realizó durante el día y con luz artificial, otras pruebas se realizaron con otras condiciones de iluminación y en todas se encontraba que existía una señal de error, por la iluminación del medio ambiente. Esto muestra la sensibilidad del sensor de visión lineal CCD.

Finalmente, una última prueba se muestra enla Fig. 11. En esta prueba, realizada de día y con iluminación artificial, se bloqueó la luz que incide al sensor utilizando una banda de cartón.

Julio C. Sosa, Iván Dominguez-Lopez, Adrián L. García-García, J. D. Oscar Barceinas-Sánchez, et al.

Fig. 11. Visualización de la interfaz con la señal del sensor CCD.

Esta prueba fue hecha así con la intención de observar el off-set que se agrega con la luz del medio ambiente. La señal se despliega en la ventana de la interfaz de la computadora.

# 5. Resultados y conclusiones

El diseño de la arquitectura, que controla y gestiona la información, se implementó en un FPGA; Cyclone IV de Altera. Sólo se empleó el 26% de sus elementos lógicos y el 48% de sus terminales, como indica el resultado de la simulación y síntesis de la Fig. 12.

| Flow Summary                       |                                                 |

|------------------------------------|-------------------------------------------------|

| Flow Status                        | Successful - Sun Jul 12 15:56:21 2015           |

| Quartus II 32-bit Version          | 13.0.1 Build 232 06/12/2013 SP 1 SJ Web Edition |

| Revision Name                      | DE0_NANO                                        |

| Top-level Entity Name              | DE0_NANO                                        |

| Family                             | Cyclone IV E                                    |

| Device                             | EP4CE22F17C6                                    |

| Timing Models                      | Final                                           |

| Total logic elements               | 5,907 / 22,320 ( 26 % )                         |

| Total combinational functions      | 5,206 / 22,320 ( 23 % )                         |

| Dedicated logic registers          | 3,858 / 22,320 ( 17 % )                         |

| Total registers                    | 3927                                            |

| Total pins                         | 74 / 154 ( 48 % )                               |

| Total virtual pins                 | 0                                               |

| Total memory bits                  | 196,352 / 608,256 ( 32 % )                      |

| Embedded Multiplier 9-bit elements | 4 / 132 ( 3 % )                                 |

| Total PLLs                         | 1/4(25%)                                        |

|                                    |                                                 |

Fig. 12. Resultado de la compilación y síntesis.

Se diseñaron dos circuitos PCB's de los cuales en uno se incorpora el sensor de visión lineal CCD y el otro contiene el conector DB9 y su circuito controlador MAX232. Estos PCB's se muestran en la Fig. 13. El sistema adquiere y muestra, la luz láser esparcida, a través de la interfaz de visualización. La interfaz puede almacenar, en el computador principal, la información en caso de que se quiere graficar posteriormente. La información graficada incorpora el ruido del medio ambiente.

Fig. 13. PCB's del sistema embebido interconectados con la tarjeta DE0-Nano.

El sistema embebido diseñado detecta la luz láser esparcida analógica y es convertida y procesada en la tarjeta de desarrollo DEO-Nano. Posteriormente es transmitida mediante el puerto UART hacía la computadora en donde es graficada la señal. Se presenta el inconveniente de que la sensibilidad de sensor de visión lineal CCD es tal que al funcionar durante el día o con iluminación artificial existe una señal incorporada a la señal de la luz láser esparcida. Por tal razón se propone agregar o incorporar un filtro para separar la luz del ambiente y leer sólo la luz láser esparcida.

**Agradecimientos.** Este trabajo ha sido financiado por la Secretaria de Investigación y Posgrado del IPN, con el proyecto de número de registro SIP: 20151013.

## Referencias

- 1. Dominguez, I., Huerta, J.A., Montes, R.I.: Mediciones de cambio de intensidad en luz laser esparcida, aplicada al monitoreo de desgaste. Simposio de metrología, pp. 1–5 (2006)

- 2. AST G 99-05: Standard Test Method for Wear Testing with a Pin-on-Disc Apparatus. ASTM International. www.astm.org (2015)

- 3. Martínez-Fuentes, V., Domínguez-López, I., García-García, A.L.: Surface texture changes followed-up in real time during the initial wear transient of dry sliding of

- steel against several metals using laser light scattering, Wear, Vol. 271, pp. 994–998 (2011)

- 4. Moreno, A., Miramontes, G., Sifuentes, C., García, E., Huerta, J.A.: Una Herramienta Computacional para Simulación del Esparcimiento de Luz Láser en Superificies Rugosas, Revista Colombiana de Física, Vol. 43, No. 1 (2011)

- 5. Martínez Fuentes, V. Domínguez López, I., García García A.L.: Estudio teórico-experimental del esparcimiento de luz láser por superficies sometidas a desgaste, p.p. 371 (1–6), CIINDET (2008)

- 6. Yong, Q., Zhen, Z.: Study of Measurement of Protein Content Based on Laser Light Scattering Technology. International Conference on Control, Automation and Systems Engineering (CASE), pp. 1–4 (Julio 2011)

- 7. Ortiz, J.D.: Desarrollo y Aplicación de Instrumentación para la Medición de Esparcimiento de Luz Láser. Instituto Politecnico Nácional, CICATA-QRO, Tesis Doctoral, (Junio 2010)

- 8. Toshiba: Data Sheet: CCD Linear Image Sensor TCD1304AP (2001)

- 9. Galeano, G.: Programación de sistemas embebidos en C. Alfaomega Grupo Editor, S.A. de C.V. (2011)

- 10. https://www.raspberrypi.org/

- 11. Angulo, J.M., Angulo, I., Etxebarría, A.: Microcontroladores PIC: Diseño práctico de aplicaciones. Mc. Graw Hill (2007)

- 12. Sosa, J.C., Martínez, Y., García, V., Hernández, R.: Estudio y elección de un softcore para la enseñanza de sistemas embebidos. 24a. Reunión internacional de otoño de comunicaciones, computación, electrónica, automatización, robótica y exposición industrial, ROC&C. Ponencia 50 (2013)

- 13. Gajski, D.D., Abdi, S., Gerstlauer, A., Schirner, G.: Embedded System Design: Modeling, Synthesis and Verification, Springer (2009)

- 14. Altera: Nios II Software Developer's Handbook: Getting Started with the Graphical User Interface (January 2014)

- 15. Texas Instruments: MAX232x Dual EIA-232 Driver/Receivers (2014)